# 3MHz Dual 1.5A Step-Down Converters and Dual Low-Input LDOs with I<sup>2</sup>C Compatible Interface

### **ISL9305H**

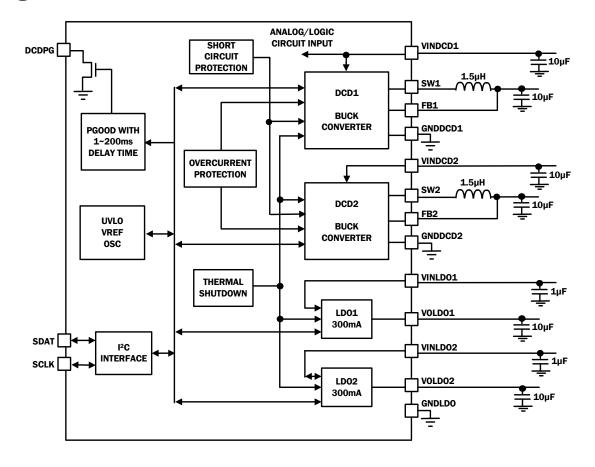

ISL9305H is an integrated mini Power Management IC (mini-PMIC) for powering low-voltage microprocessor, or applications using a single Li-lon or Li-Polymer cell battery to power multiple voltage rails. ISL9305H integrates two high-efficiency 3MHz synchronous step-down converters (DCD1 and DCD2) and two low-input, low-dropout linear regulators (LD01 and LD02).

The 3MHz PWM switching frequency allows the use of very small external inductors and capacitors. Both step-down converters can enter skip mode under light load conditions to further improve the efficiency and maximize the battery life. For noise sensitive applications, they can also be programmed through  $\rm I^2C$  interface to operate in forced PWM mode regardless of the load current condition. The  $\rm I^2C$  interface supports on-the-fly slew rate control of the output voltage from 0.825V to 3.6V at 25mV/step size for dynamic power saving. Each step-down converter can supply up to 1.5A load current. The default output voltage can be set from 0.8V to VIN using external feedback resistors on the adjustable version, or the ISL9305H can be ordered in factory pre-set power-up default voltages in increments of 100mV from 0.9V to 3.6V.

ISL9305H also provides two 300mA low dropout (LDO) regulators. The input voltage range is 1.5V to 5.5V allowing them to be powered from one of the on-chip step-down converters or directly from the battery. The default LDO output comes with factory pre-set fixed output voltage options between 0.9V to 3.3V.

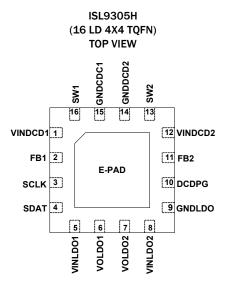

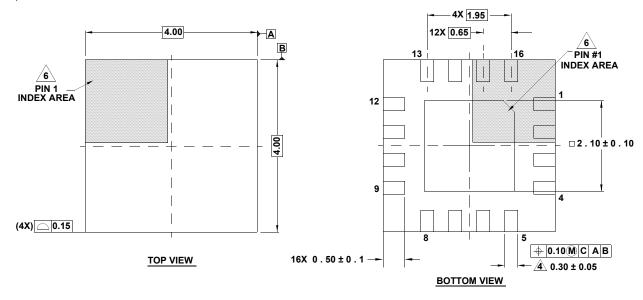

ISL9305H is available in a 4mmx4mm 16 Ld TQFN package.

### **Related Literature**

- FN7605, ISL9305 Data Sheet

- AN1564 "ISL9305IRTZEVAL1Z and ISL9305HIRTZEVAL1Z Evaluation Boards"

### **Features**

- Dual 1.5A, Synchronous Step-down Converters and Dual 300mA, General-purpose LDOs

- · Input Voltage Range

- 400kb/s I<sup>2</sup>C-Bus Series Interface Transfers the Control Data Between the Host Controller and the ISL9305H

- Adjustable Output Voltage

- DCD1/DCD2 . . . . . . . . . . . . . . . 0.8V to V<sub>IN</sub>

- Fixed Output I<sup>2</sup>C Programmability

- LD01/LD02 Output Voltage I<sup>2</sup>C Programmability

- 50 $\mu$ A I $_{\rm Q}$  (Typ) with DCD1/DCD2 in Skip Mode; 20 $\mu$ A I $_{\rm Q}$  (Typ) for Each Enabled LDO

- On-the-fly I<sup>2</sup>C Programming of DC/DC and LDO Output Voltages

- DCD1/DCD2 I<sup>2</sup>C Programmable Skip Mode Under Light Load or Forced Fixed Switching Frequency PWM Mode

- Small, Thin 4mmx4mm TQFN Package

# **Applications**

- · Cellular Phones, Smart Phones

- · PDAs, Portable Media Players, Portable Instruments

- Single Li-Ion/Li-Polymer Battery-Powered Equipment

- DSP Core Power

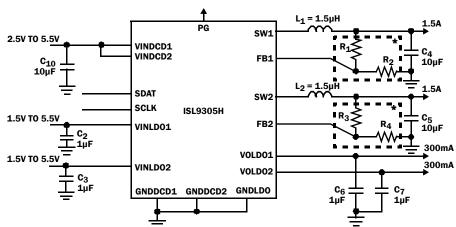

\*ONLY FOR ADJUSTABLE OUTPUT VERSION. FOR FIXED OUTPUT VERSION, DIRECTLY CONNECT THE FB PIN TO THE OUTPUT OF THE BUCK CONVERTER.

FIGURE 1. TYPICAL APPLICATION DIAGRAM

**TABLE 1. TYPICAL APPLICATION PART LIST**

| PARTS             | DESCRIPTION      | MANUFACTURER | PART NUMBER        | SPECIFICATIONS   | SIZE               |

|-------------------|------------------|--------------|--------------------|------------------|--------------------|

| L1, L2            | Inductor         | Sumida       | CDRH2D14NP-1R5     | 1.5μH/1.80A/50mΩ | 3.0mmx3.0mmx1.55mm |

| C1                | Input capacitor  | Murata       | GRM21BR60J106KE19L | 10µF/6.3V        | 0805               |

| C2, C3            | Intput capacitor | Murata       | GRM185R60J105KE26D | 1μF/6.3V         | 0603               |

| C4, C5            | Output capacitor | Murata       | GRM21BR71A106KE51L | 10µF/6.3V        | 0805               |

| C6, C7            | Output capacitor | Murata       | GRM185R60J105KE26D | 1μF/6.3V         | 0603               |

| R1, R2,<br>R3, R4 | Resistor         | Various      |                    | 1%, SMD, 0.1W    | 0603               |

# **Pin Configuration**

# **Pin Descriptions**

| PIN NUMBER<br>(TQFN) | NAME    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | VINDCD1 | Input voltage for buck converter DCD1 and it also serves as the power supply pin for the whole internal digital/analog circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2                    | FB1     | Feedback pin for DCD1, connect external voltage divider resistors between DCDC1 output, this pin and ground. For fixed output versions, connect this pin directly to the DCD1 output.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3                    | SCLK    | I <sup>2</sup> C interface clock pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4                    | SDAT    | I <sup>2</sup> C interface data pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5                    | VINLD01 | Input voltage for LDO1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6                    | VOLD01  | Output voltage of LDO1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7                    | VOLD02  | Output voltage of LD02.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8                    | VINLD02 | Input voltage for LDO2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9                    | GNDLDO  | Power ground for LD01 and LD02.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10                   | DCDPG   | The DCDPG pin is an open-drain output to indicate the state of the DCD1/DCD2 output voltages. When both DCD1 and DCD2 are enabled, the output is released to be pulled high by an external pull-up resistor if both converter voltages are within the power good range. The pin will be pulled low if either DCD is outside their range. When only one DCD is enabled, the state of the enabled DCD's output will define the state of the DCDPG pin. The DCDPG state can be programmed for a delay of up to 200ms before being released to rise high. The programming range is 1ms~200ms through the I <sup>2</sup> C interface. |

# Pin Descriptions (Continued)

| PIN NUMBER<br>(TQFN) | NAME    | DESCRIPTION                                                                                                                                                                          |

|----------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11                   | FB2     | Feedback pin for DCD2, connect external voltage divider resistors between DCD2 output, this pin and ground. For fixed output versions, connect this pin directly to the DCD2 output. |

| 12                   | VINDCD2 | Input voltage for buck converter DCD2.                                                                                                                                               |

| 13                   | SW2     | Switching node for DCD2, connect to one terminal of the inductor.                                                                                                                    |

| 14                   | GNDDCD2 | Power ground for DCD2.                                                                                                                                                               |

| 15                   | GNDDCD1 | Power ground for DCD1.                                                                                                                                                               |

| 16                   | SW1     | Switching node for DCD1, connect to one terminal of the inductor.                                                                                                                    |

| E-PAD                | E-PAD   | Exposed Pad. Connect to system ground.                                                                                                                                               |

# **Block Diagram**

# **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | FBSEL<br>DCD1<br>(V) | FBSEL<br>DCD2<br>(V) | SLV<br>LD01<br>(V) | SLV<br>LDO2<br>(V) | TEMP. RANGE<br>(°C) | PACKAGE<br>(Pb-free) | PKG.<br>DWG. # |

|--------------------------------|-----------------|----------------------|----------------------|--------------------|--------------------|---------------------|----------------------|----------------|

| ISL9305IRTHAANLZ-T             | 9305I HAANLZ    | Adj                  | Adj                  | 3.3                | 2.9                | -40 to +85          | 16 Ld TQFN           | L16.4x4G       |

| ISL9305IRTHWBNLZ-T             | 9305I HWBNLZ    | 1.2                  | 1.5                  | 3.3                | 2.9                | -40 to +85          | 16 Ld TQFN           | L16.4x4G       |

| ISL9305IRTHWCLBZ-T             | 9305I HWCLBZ    | 1.2                  | 1.8                  | 2.9                | 1.5                | -40 to +85          | 16 Ld TQFN           | L16.4x4G       |

| ISL9305IRTHWCNYZ-T             | 9305I HWCNYZ    | 1.2                  | 1.8                  | 3.3                | 0.9                | -40 to +85          | 16 Ld TQFN           | L16.4x4G       |

| ISL9305IRTHWCNLZ-T             | 9305I HWCNLZ    | 1.2                  | 1.8                  | 3.3                | 2.9                | -40 to +85          | 16 Ld TQFN           | L16.4x4G       |

| ISL9305IRTHWLNCZ-T             | 9305I HWLNCZ    | 1.2                  | 2.9                  | 3.3                | 1.8                | -40 to +85          | 16 Ld TQFN           | L16.4x4G       |

| ISL9305IRTHBCNLZ-T             | 9305I HBCNLZ    | 1.5                  | 1.8                  | 3.3                | 2.9                | -40 to +85          | 16 Ld TQFN           | L16.4x4G       |

| ISL9305IRTHBFNCZ-T             | 9305I HBFNCZ    | 1.5                  | 2.5                  | 3.3                | 1.8                | -40 to +85          | 16 Ld TQFN           | L16.4x4G       |

### NOTES:

- 1. Please refer to <a>TB347</a> for details on reel specifications.

- These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte

tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pbfree products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL9305H. For more information on MSL please see techbrief TB363.

### **Absolute Maximum Ratings** (Refer to ground)

| SW1, SW21.5V to 6                                | .5٧ |

|--------------------------------------------------|-----|

| FB1, FB20.3V to 3                                | .6٧ |

| GNDDCD1, GNDDCD2, GNDLD00.3V to 0                | .3۷ |

| All other pins0.3V to 6                          | .5۷ |

| ESD Ratings                                      |     |

| Human Body Model (Tested per JESD22-A114F)3.5    | 5kV |

| Machine Model (Tested per JESD22-A115-A) 2.2     | 2kV |

| Charged Device Model (Tested per JESD22-C101D)   | 25∨ |

| Latch Up (Tested per JESD78B, Class II, Level A) | mΑ  |

|                                                  |     |

### **Thermal Information**

| Thermal Resistance (Typical)             | $\theta_{JA}$ (°C/W) | θ <sub>JC</sub> (°C/W) |

|------------------------------------------|----------------------|------------------------|

| 16 Ld TQFN Package (Notes 4, 5)          | 42                   | 5                      |

| Maximum Junction Temperature Range       | 4                    | 0°C to +150°C          |

| Recommended Junction Temperature Range   | ·                    | 0°C to +125°C          |

| Storage Temperature Range                | 4                    | 0°C to +150°C          |

| Pb-free reflow profile                   |                      | see link below         |

| http://www.intersil.com/pbfree/Pb-FreeRe | eflow.asp            |                        |

### **Recommended Operating Conditions**

| VINDCD1                       | 2.5V to 5.5V    |

|-------------------------------|-----------------|

| VINDCD2                       | 2.5V to VINDCD1 |

| VINLD01 and VINLD02           | 1.5V to VINDCD1 |

| DCD1 and DCD2 Output Current  | 0A to 1.5A      |

| LD01 and LD02 Output Current  | 0mA to 300mA    |

| Operating Ambient Temperature | 40°C to +85°C   |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

### NOTES:

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 5.  $\theta_{\text{JC}}$ , "case temperature" location is at the center of the exposed metal pad on the package underside.

Electrical Specifications Unless otherwise noted, all parameter limits are guaranteed over the recommended operating conditions and the typical specifications are measured at the following conditions:  $T_A = +25$  °C, VINDCD1 = 3.6V, VINDCD2 = 3.3V. For LDO1 and LDO2, VINLDOx = VOLDOx + 0.5V to 5.5V with VINLDOx always no higher than VINDCD1,  $L1 = L2 = 1.5 \mu H$ ,  $C1 = 10\mu F$ ,  $C4 = C5 = 10\mu F$ ,  $C2 = C3 = C6 = C7 = 1\mu F$ , IOUT = 0A for DCD1, DCD2, LDO1 and LDO2 (see "TYPICAL APPLICATION DIAGRAM" on page 1 for more details).

| PARAMETER                                                                                                 | SYMBOL            | TEST CONDITIONS                                                                                           | MIN<br>(Note 6) | TYP   | MAX<br>(Note 6) | UNIT |

|-----------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------|-----------------|-------|-----------------|------|

| VINDCD1, VINDCD2 Voltage Range                                                                            |                   |                                                                                                           | 2.5             | -     | 5.5             | ٧    |

| VINDCD1, VINDCD2 Undervoltage                                                                             | V <sub>UVLO</sub> | Rising                                                                                                    | -               | 2.2   | 2.3             | V    |

| Lockout Threshold                                                                                         |                   | Falling                                                                                                   | 1.9             | 2.1   | -               | V    |

| Quiescent Supply Current on VINDCD1 I <sub>VIN1</sub> Only DCD1 enabled, no load and no switching on DCD1 |                   | -                                                                                                         | 40              | 60    | μΑ              |      |

|                                                                                                           | I <sub>VIN2</sub> | Only DCD1 and LDO1 enabled, with no load and no switching on DCD1                                         | -               | 60    | 95              | μA   |

|                                                                                                           | I <sub>VIN3</sub> | Both DCD1 and DCD2 enabled, no load and no switching on both DCD1 and DCD2                                | -               | 50    | 75              | μΑ   |

|                                                                                                           | I <sub>VIN4</sub> | Only LD01 and LD02 enabled                                                                                | -               | 75    | 100             | μΑ   |

|                                                                                                           | I <sub>VIN5</sub> | DCD1, DCD2, LD01 and LD02 are enabled, with no load and no switching on both DCD1 and DCD2                | -               | 100   | 130             | μΑ   |

|                                                                                                           | I <sub>VIN6</sub> | Only one DCD in forced PWM mode, no load                                                                  | -               | 4     | 7.5             | mA   |

| Shutdown Supply Current                                                                                   | I <sub>SD</sub>   | VINDCD1 = 5.5V, DCD1, DCD2, LDO1 and LDO2 are disabled through I <sup>2</sup> C interface, VINDCD1 = 4.2V |                 | 0.15  | 5               | μΑ   |

| Thermal Shutdown                                                                                          |                   |                                                                                                           | -               | 155   | -               | °C   |

| Thermal Shutdown Hysteresis                                                                               |                   |                                                                                                           | -               | 30    | -               | °C   |

| DCD1 AND DCD2                                                                                             |                   |                                                                                                           |                 |       |                 |      |

| FB1, FB2 Regulation Voltage                                                                               | V <sub>FB</sub>   |                                                                                                           | 0.785           | 0.8   | 0.815           | V    |

| FB1, FB2 Bias Current                                                                                     | I <sub>FB</sub>   | FB = 0.75V                                                                                                |                 | 0.001 | -               | μΑ   |

| Output Voltage Accuracy                                                                                   |                   | V <sub>IN</sub> = V <sub>O</sub> + 0.5V to 5.5V (minimal 2.5V), 1mA load                                  | -3              | -     | +3              | %    |

| Line Regulation                                                                                           |                   | V <sub>IN</sub> = V <sub>0</sub> + 0.5V to 5.5V (minimal 2.5V)                                            | -               | 0.1   | -               | %/V  |

intersil FN7724.0 November 8, 2010

Electrical Specifications Unless otherwise noted, all parameter limits are guaranteed over the recommended operating conditions and the typical specifications are measured at the following conditions:  $T_A = +25$  °C, VINDCD1 = 3.6V, VINDCD2 = 3.3V. For LDO1 and LDO2, VINLDOx = VOLDOx + 0.5V to 5.5V with VINLDOx always no higher than VINDCD1, L1 = L2 =  $1.5\mu$ H,  $C1 = 10 \mu F$ ,  $C4 = C5 = 10 \mu F$ ,  $C2 = C3 = C6 = C7 = 1 \mu F$ , IOUT = 0A for DCD1, DCD2, LDO1 and LDO2 (see "TYPICAL") APPLICATION DIAGRAM" on page 1 for more details). (Continued)

| PARAMETER                           | SYMBOL            | TEST CONDITIONS                                                                                        | MIN<br>(Note 6) | TYP   | MAX<br>(Note 6) | UNIT              |

|-------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------|-----------------|-------|-----------------|-------------------|

| Maximum Output Current              |                   |                                                                                                        | 1500            | -     | -               | mA                |

| P-Channel MOSFET ON-resistance      |                   | V <sub>IN</sub> = 3.6V, I <sub>O</sub> = 200mA                                                         | -               | 0.14  | 0.20            | Ω                 |

|                                     |                   | V <sub>IN</sub> = 2.3V, I <sub>O</sub> = 200mA                                                         | -               | 0.24  | 0.40            | Ω                 |

| N-Channel MOSFET ON-resistance      |                   | V <sub>IN</sub> = 3.6V, I <sub>O</sub> = 200mA                                                         | -               | 0.11  | 0.20            | Ω                 |

|                                     |                   | V <sub>IN</sub> = 2.3V, I <sub>O</sub> = 200mA                                                         |                 | 0.18  | 0.34            | Ω                 |

| P-Channel MOSFET Peak Current Limit | I <sub>PK</sub>   |                                                                                                        | 2.1             | 2.5   | 2.75            | Α                 |

| SW Maximum Duty Cycle               |                   |                                                                                                        | -               | 100   | -               | %                 |

| SW Leakage Current                  |                   | V <sub>IN</sub> = 5.5V                                                                                 | -               | 0.005 | 1               | μΑ                |

| PWM Switching Frequency             | f <sub>S</sub>    |                                                                                                        | 2.6             | 3.0   | 3.4             | MHz               |

| SW Minimum ON-time                  |                   | V <sub>FB</sub> = 0.75V                                                                                | -               | 70    | -               | ns                |

| Bleeding Resistor                   |                   |                                                                                                        | -               | 115   | -               | Ω                 |

| PG                                  | -                 |                                                                                                        |                 |       |                 | <u>I</u>          |

| Output Low Voltage                  |                   | Sinking 1mA, FB1 = FB2 = 0.7V                                                                          | -               | -     | 0.25            | V                 |

| Rising Delay Time                   |                   | Based on 1ms programmed nominal delay time                                                             | 0.6             | 1.1   | 1.8             | ms                |

| Falling Delay Time                  |                   | Based on 1ms programmed nominal delay time                                                             | -               | 30    | -               | μs                |

| PG Pin Leakage Current              |                   | PG = VINDCD1 = VINDCD2 = 3.6V                                                                          | -               | 0.005 | 0.1             | μΑ                |

| PG Low Rising Threshold             |                   | Percentage of nominal regulation voltage                                                               | -               | 91    | -               | %                 |

| PG Low Falling Threshold            |                   | Percentage of nominal regulation voltage                                                               | -               | 87    | -               | %                 |

| PG High Rising Threshold            |                   | Percentage of nominal regulation voltage                                                               | -               | 112   | -               | %                 |

| PG High Falling Threshold           |                   | Percentage of nominal regulation voltage                                                               | -               | 109   | -               | %                 |

| LD01 AND LD02                       |                   |                                                                                                        |                 | ı     |                 | <u> </u>          |

| VINLDO1, VINLDO2 Supply Voltage     |                   | No higher than VINDCD1                                                                                 | 1.5             | -     | 5.5             | V                 |

| VINLDO1, VINLDO2 Undervoltage       | V <sub>UVLO</sub> | Rising                                                                                                 | -               | 1.41  | 1.46            | V                 |

| Lockout Threshold                   |                   | Falling                                                                                                | 1.33            | 1.37  | -               | V                 |

| Internal Peak Current Limit         |                   |                                                                                                        | 350             | 425   | 540             | mA                |

| Dropout Voltage                     |                   | I <sub>0</sub> = 300mA, V <sub>0</sub> ≤ 2.1V                                                          | -               | 120   | 250             | mV                |

|                                     |                   | $I_0 = 300 \text{mA}, 2.1 \text{V} < \text{V}_0 \le 2.8 \text{V}$                                      | -               | 100   | 200             | mV                |

|                                     |                   | I <sub>0</sub> = 300mA, V <sub>0</sub> > 2.8V                                                          | -               | 80    | 170             | mV                |

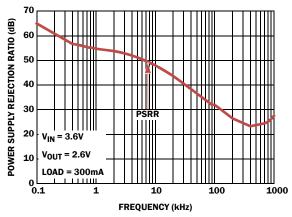

| Power Supply Rejection Ratio        |                   | I <sub>O</sub> = 300mA @ 1kHz, V <sub>IN</sub> = 3.6V, V <sub>O</sub> = 2.6V, T <sub>A</sub> = +25 ° C | -               | 55    | -               | dB                |

| Output Voltage Noise                |                   | V <sub>IN</sub> = 4.2V, I <sub>O</sub> = 10mA, T <sub>A</sub> = +25 °C, BW = 10Hz to 100kHz            | -               | 45    | -               | μV <sub>RMS</sub> |

### NOTE:

<sup>6.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

# **Theory of Operation**

### **DCD1** and **DCD2** Introduction

Both the DCD1 and DCD2 converters on ISL9305H use the peak-current-mode pulse-width modulation (PWM) control scheme for fast transient response and pulse-by-pulse current limiting. Both converters are able to supply up to 1.5A load current. The default output voltage ranges from 0.8V to 3.6V depending on the factory pre-set configuration and can be programmed via the  $\rm I^2C$  interface in the range of 0.825V to 3.6V at 25mV/step with a programmable slew rate. An open-drain DCDPG (DCD Power-Good) signal is also provided to monitor the DCD1 and DCD2 output voltages. Optionally, both DCD1 and DCD2 can be programmed to be actively discharged via an on-chip bleeding resistor (typical  $115\Omega$ ) when the converter is disabled.

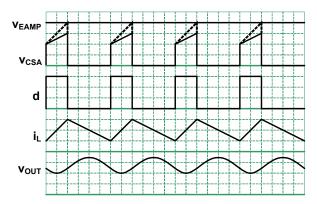

### Skip Mode (PFM Mode) for DCD1/DCD2

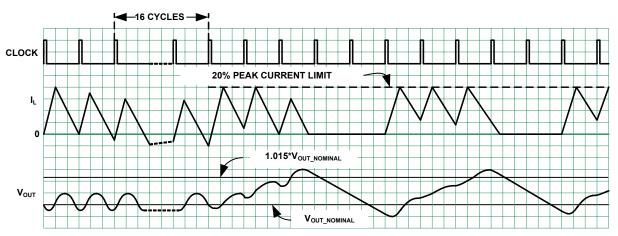

Under light load condition, the DCD1 and DCD2 can be programmed to automatically enter a pulse-skipping mode to minimize the switching loss by reducing the switching frequency. Figure 3 illustrates the skip mode operation. A zero-cross sensing circuit monitors the current flowing through SW node for zero crossing. When it is detected to cross zero for 16 consecutive cycles, the regulator enters the skip mode. During the 16 consecutive cycles. the inductor current could be negative. The counter is reset to zero when the sensed current flowing through SW node does not cross zero during any cycle within the 16 consecutive cycles. Once the converter enters the skip mode, the pulse modulation is controlled by an internal comparator while each pulse cycle remains synchronized to the PWM clock. The P-Channel MOSFET is turned on at the rising edge of the clock and turned off when its current reaches ~20% of the peak current limit. As the average inductor current in each cycle is higher than the average current of the load, the output voltage rises cycle-over-cycle. When the output voltage is sensed to reach 1.5% above its nominal voltage, the P-Channel MOSFET is turned off immediately and the inductor current is fully discharged to zero and stays at zero. The output voltage reduces gradually due to the load current discharging the output capacitor. When the output voltage drops to the nominal voltage, the P-Channel MOSFET will be turned on again, repeating the previous operations.

FIGURE 2. PWM OPERATION WAVEFORMS

The regulator resumes normal PWM mode operation when the output voltage is sensed to drop below 1.5% of its nominal voltage value.

### **Soft-Start**

The soft-start reduces the in-rush current during the start-up stage. The soft-start block limits the current rising speed so that the output voltage rises in a controlled fashion.

### **Overcurrent Protection**

The overcurrent protection for DCD1 and DCD2 is provided on ISL9305H for when an overload condition occurs. When the current at P-Channel MOSFET is sensed to reach the current limit, the internal protection circuit is triggered to turn off the P-Channel MOSFET immediately.

### **DCD Short-Circuit Protection**

The ISL9305H provides Short-Circuit Protection for both DCD1 and DCD2. The feedback voltage is monitored for output short-circuit protection. When the output voltage is sensed to be lower than a certain threshold, the internal circuit will change the PWM oscillator frequency to a lower frequencies in order to protect the IC from damage. The P-Channel MOSFET peak current limit remains active during this state.

FIGURE 3. SKIP MODE OPERATION WAVEFORMS

### **Undervoltage Lockout (UVLO)**

An undervoltage lockout (UVLO) circuit is provided on ISL9305H. The UVLO circuit block can prevent abnormal operation in the event that the supply voltage is too low to guarantee proper operation. The UVLO on VINDCD1 is set for a typical 2.2V with 100mV hysteresis. VINLDO1 and VINLDO2 are set for a typical 1.4V with 50mV hysteresis. When the input voltage is sensed to be lower than the UVLO threshold, the related channel is disabled.

### **DCDPG (DCD Power-Good)**

ISL9305H offers an open-drain Power-Good signal with programmable delay time for monitoring the converters DCD1 and DCD2 output voltages status.

When both DCD1 and DCD2 are enabled and their output voltages are within the power-good window, an internal power-good signal is issued to turn off the open-drain MOSFET so the DCDPG pin voltage can be externally pulled high after a programmed delay time. If either DCD1 or DCD2 output voltages or both of them are not within the power-good window, the DCDPG outputs an open-drain logic low signal after the programmed delay time.

When there is only one DCD converter (either DCD1 or DCD2) is enabled, then the DCDPG only indicates the status of this active DCD converter. For example, if only DCD1 converter is enabled and DCD2 converter is disabled, when DCD1 output is within the power-good window, internal power-good signal will be issued to turn off the open-drain MOSFET so the DCDPG pin voltage is externally pulled high after the programmed delay time. If output voltage of DCD1 is outside the power-good window, the DCDPG outputs an open-drain logic low signal after the programmed delay time. It is similar when only DCD2 is enabled and DCD1 is disabled. When both converters are disabled, DCDPG always outputs the open-drain logic low signal.

### **Low Dropout Operation**

Both DCD1 and DCD2 converters feature the low dropout operation to maximize the battery life. When the input voltage drops to a level that the converter can no longer operate under switching regulation to maintain the output voltage, the P-Channel MOSFET is completely turned on (100% duty cycle). The dropout voltage under such a condition is the product of the load current and the ON-resistance of the P-Channel MOSFET. Minimum required input voltage  $V_{IN}$  under such condition is the sum of output voltage plus the voltage drop across the inductor and the P-Channel MOSFET switch.

# Active Output Voltage Discharge For DCD1/DCD2

The ISL9305H offers a feature to actively discharge the output voltage of DCD1 and DCD2 via an internal bleeding resistor (typical  $115\Omega$ ) when the channel is disabled. This feature is enabled by default, but can be individually outputs can be disabled through programming the control bit in DCD\_PARAMETER register.

### **Thermal Shutdown**

The ISL9305H provides built-in thermal protection function with thermal shutdown threshold temperature set at  $+155\,^{\circ}$ C with  $+25\,^{\circ}$ C hysteresis (typical). When the die temperature is sensed to reach  $+130\,^{\circ}$ C, the regulator is completely shut down and as the temperature is sensed to drop to  $+105\,^{\circ}$ C (typical), the device resumes normal operation starting from the soft-start.

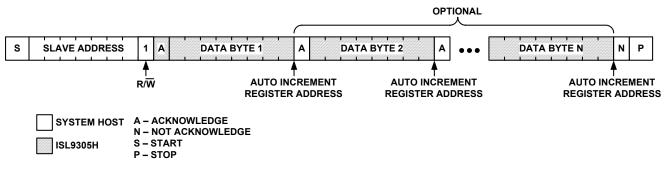

# I<sup>2</sup>C Compatible Interface

The ISL9305H offers an I<sup>2</sup>C compatible interface, using two pins: SCLK for the serial clock and SDAT for serial data respectively. According to the I<sup>2</sup>C specifications, a pull-up resistor is needed for the clock and data signals to connect to a positive supply. When the ISL9305 and the host use different supply voltages, the pull-up resistors should be connected to the higher voltage rail.

Signal timing specifications should satisfy the standard I<sup>2</sup>C bus specification. The maximum bit rate is 400kb/s and more details regarding the I<sup>2</sup>C specifications can be found from Philips.

### I<sup>2</sup>C Slave Address

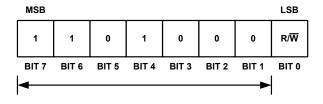

The ISL9305H serves as a slave device and the 7-bit default chip address is 1101000, as shown in Figure 4. According to the I<sup>2</sup>C specifications, here the value of Bit 0 determines the direction of the message ("0" means "write" and "1" means "read").

FIGURE 4. I<sup>2</sup>C SLAVE ADDRESS

# I<sup>2</sup>C Protocol

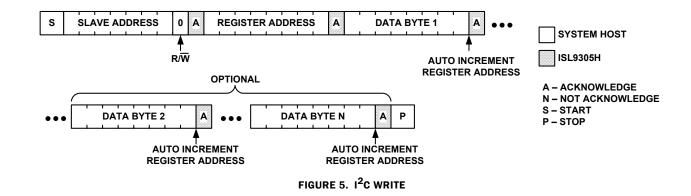

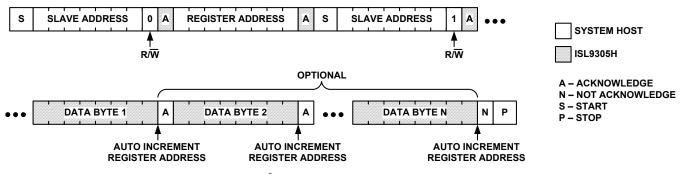

Figures 5, 6, and 7 show three typical I<sup>2</sup>C-bus transaction protocols.

FIGURE 6. I<sup>2</sup>C READ SPECIFYING REGISTER ADDRESS

FIGURE 7. I<sup>2</sup>C READ NOT SPECIFYING REGISTER ADDRESS

# I<sup>2</sup>C Control Registers

All the registers are reset at initial start-up.

### **DCD OUTPUT VOLTAGE CONTROL REGISTER**

DCD10UT, address 0x00h; DCD20UT, address 0x01h

Caution: Disable DCD prior to changing from fixed output voltage to adjustable output voltage or from adjustable output voltage to fixed output voltage using  $I^2\text{C}$ .

### TABLE 2. BUCK CONVERTERS OUTPUT VOLTAGE CONTROL REGISTER

| BIT | NAME      | ACCESS | RESET | DESCRIPTION      |

|-----|-----------|--------|-------|------------------|

| В7  | Reserve   | -      | 0     | Refer to Table 3 |

| В6  | DCDxOUT-6 | R/W    | 0     |                  |

| B5  | DCDxOUT-5 | R/W    | 0     |                  |

| В4  | DCDxOUT-4 | R/W    | 1     |                  |

| В3  | DCDxOUT-3 | R/W    | 0     | Refer to Table 3 |

| B2  | DCDxOUT-2 | R/W    | 0     |                  |

| B1  | DCDxOUT-1 | R/W    | 0     |                  |

| во  | DCDxOUT-0 | R/W    | 0     |                  |

TABLE 3. DCD1 AND DCD2 OUTPUT VOLTAGE SETTING

| DCDOUT<br><7:0> | DCD OUTPUT<br>VOLTAGE<br>(V) |

|-----------------|------------------------------|-----------------|------------------------------|-----------------|------------------------------|-----------------|------------------------------|

| 00              | 0.825                        | 20              | 1.625                        | 40              | 2.425                        | 60              | 3.225                        |

| 01              | 0.850                        | 21              | 1.650                        | 41              | 2.450                        | 61              | 3.250                        |

| 02              | 0.875                        | 22              | 1.675                        | 42              | 2.475                        | 62              | 3.275                        |

| 03              | 0.900                        | 23              | 1.700                        | 43              | 2.500                        | 63              | 3.300                        |

| 04              | 0.925                        | 24              | 1.725                        | 44              | 2.525                        | 64              | 3.325                        |

| 05              | 0.950                        | 25              | 1.750                        | 45              | 2.550                        | 65              | 3.350                        |

| 06              | 0.975                        | 26              | 1.775                        | 46              | 2.575                        | 66              | 3.375                        |

| 07              | 1.000                        | 27              | 1.800                        | 47              | 2.600                        | 67              | 3.400                        |

| 08              | 1.025                        | 28              | 1.825                        | 48              | 2.625                        | 68              | 3.425                        |

| 09              | 1.050                        | 29              | 1.850                        | 49              | 2.650                        | 69              | 3.450                        |

| 0A              | 1.075                        | 2A              | 1.875                        | 4A              | 2.675                        | 6A              | 3.475                        |

| 0B              | 1.100                        | 2B              | 1.900                        | 4B              | 2.700                        | 6B              | 3.500                        |

| ОС              | 1.125                        | 2C              | 1.925                        | 4C              | 2.725                        | 6C              | 3.525                        |

| 0D              | 1.150                        | 2D              | 1.950                        | 4D              | 2.750                        | 6D              | 3.550                        |

| 0E              | 1.175                        | 2E              | 1.975                        | 4E              | 2.775                        | 6E              | 3.575                        |

| 0F              | 1.200                        | 2F              | 2.000                        | 4F              | 2.800                        | 6F              | 3.600                        |

| 10              | 1.225                        | 30              | 2.025                        | 50              | 2.825                        |                 |                              |

| 11              | 1.250                        | 31              | 2.050                        | 51              | 2.850                        |                 |                              |

| 12              | 1.275                        | 32              | 2.075                        | 52              | 2.875                        |                 |                              |

| 13              | 1.300                        | 33              | 2.100                        | 53              | 2.900                        |                 |                              |

| 14              | 1.325                        | 34              | 2.125                        | 54              | 2.925                        |                 |                              |

| 15              | 1.350                        | 35              | 2.150                        | 55              | 2.950                        |                 |                              |

| 16              | 1.375                        | 36              | 2.175                        | 56              | 2.975                        |                 |                              |

| 17              | 1.400                        | 37              | 2.200                        | 57              | 3.000                        |                 |                              |

| 18              | 1.425                        | 38              | 2.225                        | 58              | 3.025                        |                 |                              |

| 19              | 1.450                        | 39              | 2.250                        | 59              | 3.050                        |                 |                              |

| <b>1</b> A      | 1.475                        | ЗА              | 2.275                        | 5A              | 3.075                        |                 |                              |

| 1B              | 1.500                        | 3B              | 2.300                        | 5B              | 3.100                        |                 |                              |

| 1C              | 1.525                        | 3C              | 2.325                        | 5C              | 3.125                        |                 |                              |

| 1D              | 1.550                        | 3D              | 2.350                        | 5D              | 3.150                        |                 |                              |

| 1E              | 1.575                        | 3E              | 2.375                        | 5E              | 3.175                        |                 |                              |

| 1F              | 1.600                        | 3F              | 2.400                        | 5F              | 3.200                        |                 |                              |

# LDO1 AND LDO2 OUTPUT VOLTAGE CONTROL REGISTERS

LD010UT, address 0x02h and LD020UT, address 0x03h.

### TABLE 4. LDOX OUTPUT VOLTAGE CONTROL REGISTERS

| BIT | NAME      | ACCESS | RESET | DESCRIPTION             |

|-----|-----------|--------|-------|-------------------------|

| В7  | Reserve   | -      | 0     | Refer to Table 5 for    |

| В6  | Reserve   | -      | 0     | output voltage settings |

| В5  | LD0x0UT-5 | R/W    | 0     | _                       |

| В4  | LD0x0UT-4 | R/W    | 0     |                         |

| вз  | LD0x0UT-3 | R/W    | 1     |                         |

| B2  | LD0x0UT-2 | R/W    | 1     |                         |

| B1  | LD0x0UT-1 | R/W    | 0     |                         |

| во  | LD0x0UT-0 | R/W    | 0     |                         |

### **TABLE 5. LDOX OUTPUT VOLTAGE SETTINGS**

| LD00UT<br><7:0> | LDO OUTPUT<br>VOLTAGE (V) | LDOOUT<br><7:0> | LDO OUTPUT<br>VOLTAGE (V) | LD00UT<br><7:0> | LDO OUTPUT<br>VOLTAGE (V) | LDOOUT<br><7:0> | LDO OUTPUT<br>VOLTAGE (V) |

|-----------------|---------------------------|-----------------|---------------------------|-----------------|---------------------------|-----------------|---------------------------|

| 00              | 0.9                       | 10              | 1.70                      | 20              | 2.50                      | 30              | 3.30                      |

| 01              | 0.95                      | 11              | 1.75                      | 21              | 2.55                      | 31              | 3.35                      |

| 02              | 1.00                      | 12              | 1.80                      | 22              | 2.60                      | 32              | 3.40                      |

| 03              | 1.05                      | 13              | 1.85                      | 23              | 2.65                      | 33              | 3.45                      |

| 04              | 1.1                       | 14              | 1.90                      | 24              | 2.70                      | 34              | 3.50                      |

| 05              | 1.15                      | 15              | 1.95                      | 25              | 2.75                      | 35              | 3.55                      |

| 06              | 1.20                      | 16              | 2.00                      | 26              | 2.80                      | 36              | 3.60                      |

| 07              | 1.25                      | 17              | 2.05                      | 27              | 2.85                      |                 |                           |

| 08              | 1.30                      | 18              | 2.10                      | 28              | 2.90                      |                 |                           |

| 09              | 1.35                      | 19              | 2.15                      | 29              | 2.95                      |                 |                           |

| 0A              | 1.40                      | <b>1</b> A      | 2.20                      | 2A              | 3.00                      |                 |                           |

| ОВ              | 1.45                      | 1B              | 2.25                      | 2B              | 3.05                      |                 |                           |

| OC              | 1.50                      | 10              | 2.30                      | 2C              | 3.10                      |                 |                           |

| 0D              | 1.55                      | 1D              | 2.35                      | 2D              | 3.15                      |                 |                           |

| 0E              | 1.60                      | 1E              | 2.40                      | 2E              | 3.20                      |                 |                           |

| OF              | 1.65                      | 1F              | 2.45                      | 2F              | 3.25                      |                 |                           |

### **DCD1 AND DCD2 CONTROL REGISTER**

DCD\_PARAMETER, address 0x04h

### TABLE 6. DCD\_PARAMETER REGISTER

| BIT | NAME       | ACCESS | RESET | DESCRIPTION                                                                                 |

|-----|------------|--------|-------|---------------------------------------------------------------------------------------------|

| В7  | -          | -      | 0     | Reserved                                                                                    |

| В6  | DCD_PHASE  | R/W    | 0     | DCD1 and DCD2 PWM switch selection. 0-in phase; 1 to 180° out-of-phase.                     |

| В5  | DCD2_ULTRA | R/W    | 0     | Ultrasonic feature under PFM mode for DCD2. 0-disabled; 1-enabled.                          |

| B4  | DCD1_ULTRA | R/W    | 0     | Ultrasonic feature under PFM mode for DCD1. 0-disabled; 1-enabled.                          |

| вз  | DCD2_BLD   | R/W    | 1     | Selection of DCD2 for active output voltage discharge when disabled. O-disabled; 1-enabled. |

| B2  | DCD1_BLD   | R/W    | 1     | Selection of DCD1 for active output voltage discharge when disabled. O-disabled; 1-enabled. |

| B1  | DCD2_MODE  | R/W    | 1     | Selection on DCD2 of auto PFM/PWM mode (= 1) or forced PWM mode (= 0).                      |

| В0  | DCD1_MODE  | R/W    | 1     | Selection on DCD1 of auto PFM/PWM mode (= 1) or forced PWM mode (= 0).                      |

### **SYSTEM CONTROL REGISTER**

SYS\_PARAMETER, address 0x05h

TABLE 7. SYS\_PARAMETER REGISTER

| BIT | NAME                | ACCESS | RESET | DESCRIPTION                                                |

|-----|---------------------|--------|-------|------------------------------------------------------------|

| В7  | -                   | -      | 0     | Reserved                                                   |

| В6  | I <sup>2</sup> C_EN | R/W    | 0     | I <sup>2</sup> C function enable. 0-disabled;<br>1-enabled |

| В5  | DCDPOR_1            | R/W    | 1     | DCDPG Delay Time Setting,                                  |

| В4  | DCDPOR_0            | R/W    | 0     | DCDPG[1:0]: 00 to 1ms 01 to 50ms 10 to 150ms 11 to 200m    |

| вз  | LD02_EN             | R/W    | 1     | LD02 enable selection. 0-disable,<br>1-enable.             |

| B2  | LDO1_EN             | R/W    | 1     | LD01 enable selection. 0-disable,<br>1-enable              |

| B1  | DCD2_EN             | R/W    | 1     | DCD2 enable selection. 0-disable,<br>1-enable.             |

| во  | DCD1_EN             | R/W    | 1     | DCD2 enable selection. 0-disable,<br>1-enable              |

### **DCD OUTPUT VOLTAGE SLEW RATE CONTROL REGISTER**

DCD\_SRCTL, address 0x06h

TABLE 8. DCD OUPUT VOLTAGE SLEW RATE CONTROL REGISTER

| BIT | NAME     | ACCESS | RESET | DESCRIPTION                                                                                                       |  |  |

|-----|----------|--------|-------|-------------------------------------------------------------------------------------------------------------------|--|--|

| В7  | DCD2SR_2 | R/W    | 0     | DCD2 Slew Rate Setting, DCD2SR[2:0]:                                                                              |  |  |

| В6  | DCD2SR_1 | R/W    | 0     | 000 to 0.225mV/μs<br>001 to 0.45mV/μs                                                                             |  |  |

| B5  | DCD2SR_0 | R/W    | 1     | 010 to 0.90mV/μs<br>011 to 1.8mV/μs<br>100 to 3.6mV/μs<br>101 to 7.2mV/μs<br>110 to 14.4mV/μs<br>111 to immediate |  |  |

| В4  | Reserve  | -      | 0     | Reserved                                                                                                          |  |  |

| вз  | DCD1SR_2 | R/W    | 0     | DCD1 Slew Rate Setting, DCD1SR[2:0]:                                                                              |  |  |

| B2  | DCD1SR_1 | R/W    | 0     | 000 to 0.225mV/μs<br>001 to 0.45mV/μs                                                                             |  |  |

| B1  | DCD1SR_0 | R/W    | 1     | 010 to 0.90mV/µs<br>011 to 1.8mV/µs<br>100 to 3.6mV/µs<br>101 to 7.2mV/µs<br>110 to 14.4mV/µs<br>111 to immediate |  |  |

| В0  | Reserve  | -      | 0     | Reserved                                                                                                          |  |  |

# **Typical Operating Conditions**

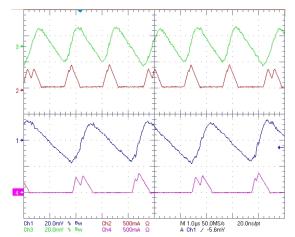

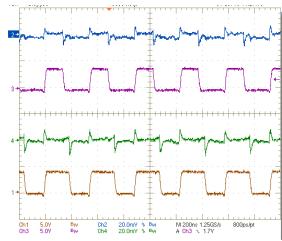

FIGURE 8. DCD OUTPUT RIPPLE ( $V_{IN}$  = 4.2V, PFM, TIME SCALE = 1 $\mu$ s) CH1: VODCD1 (20mV/DIV), CH2: IL1 (500mA/DIV), CH3: VODCD2 (20mV/DIV), CH4: IL2 (500mA/DIV)

FIGURE 10. INDUCTOR CURRENT RIPPLE ( $V_{IN}=3.6V$ , PFM, TIME SCALE = 200ns) CH1: SW1 (2V/DIV), CH2: IL1 (200mA/DIV), CH3: SW2 (2V/DIV), CH4: IL2 (200mA/DIV)

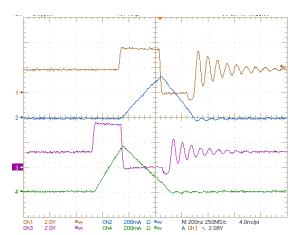

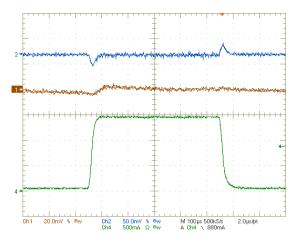

FIGURE 12. DCD1 TRANSIENT RESPONSE (V<sub>IN</sub> = 3.6V, STEP LOAD: 150mA TO 1500mA) CH1: VODCD1 (100mV/DIV, AC), CH2: VODCD2 (50mV/DIV, AC, CH4: IL4 (500mA/DIV)

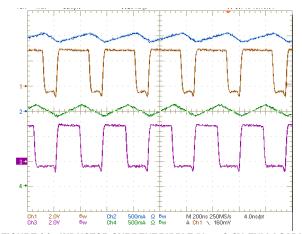

FIGURE 9. DCD OUTPUT RIPPLE ( $V_{IN}$  = 4.2V, FULL LOADING @ VODCD1 AND VODCD2, TIME SCALE = 200ns) CH1: SW1 (5V/DIV), CH2: VODCD1 (20mA/DIV), CH3: SW2 (5V/DIV), CH4: VODCD2 (20mA/DIV)

FIGURE 11. INDUCTOR CURRENT RIPPLE ( $V_{\rm IN}$  = 3.6V, FULL LOADING, PWM, TIME SCALE = 200ns) CH1: SW1 (2V/DIV), CH2: IL1 (500mA/DIV), CH3: SW2 (2V/DIV), CH4: IL2 (500mA/DIV)

FIGURE 13. DCD2 TRANSIENT RESPONSE (V<sub>IN</sub> = 3.6V, STEP LOAD: 150mA TO 1500mA) CH1: VODCD1 (100mV/DIV, AC), CH2: VODCD2 (50mV/DIV, AC, CH4: IL4 (500mA/DIV)

# **Typical Operating Conditions (Continued)**

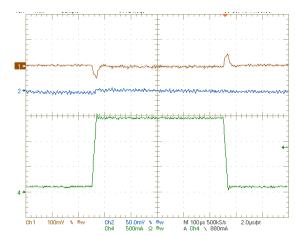

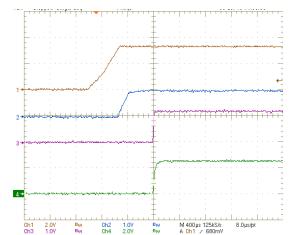

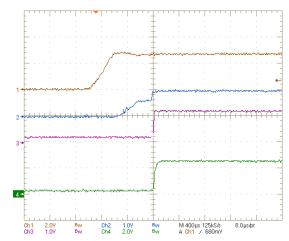

FIGURE 14. 4-CHANNEL DEFAULT START-UP @ NO LOAD CH1: VODCD1 (2V/DIV), CH2: VODCD2 (1V/DIV), CH3: VOLDO1 (1V/DIV), CH4: VOLDO2 (2V/DIV)

FIGURE 15. 4-CHANNEL DEFAULT START-UP @ FULL LOAD CH1: VODCD1 (2V/DIV), CH2: VODCD2 (1V/DIV), CH3: VOLDO1 (1V/DIV), CH4: VOLDO2 (2V/DIV)

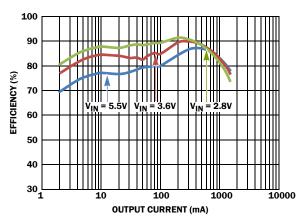

FIGURE 16. EFFICIENCY vs LOAD (V<sub>OUT</sub> = 1.8V, PFM/PWM)

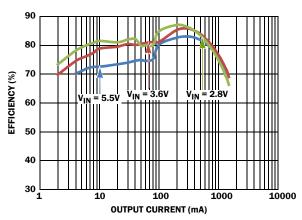

FIGURE 17. EFFICIENCY vs LOAD (Vout = 1.2V, FORCED PWM)

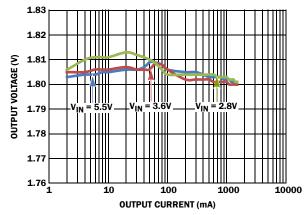

FIGURE 18. DCD OUTPUT VOLTAGE vs OUTPUT CURRENT  $(V_{OUT} = 1.8V, PFM/PWM)$

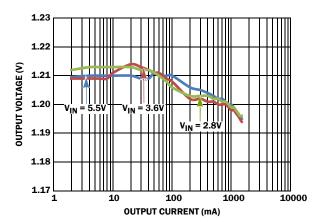

FIGURE 19. DCD OUTPUT VOLTAGE vs OUTPUT CURRENT  $(V_{OUT} = 1.2V, PFM/PWM)$

# **Typical Operating Conditions (Continued)**

FIGURE 20. RIPPLE REJECTION RATIO vs FREQUENCY

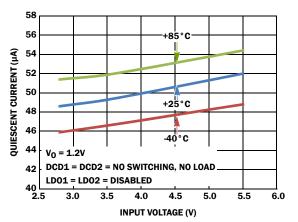

FIGURE 21. QUIESCENT CURRENT vs INPUT VOLTAGE

# **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev.

| DATE    | REVISION | CHANGE           |

|---------|----------|------------------|

| 11/8/10 | FN7724.0 | Initial Release. |

### **Products**

Intersil Corporation is a leader in the design and manufacture of high-performance analog semiconductors. The Company's products address some of the industry's fastest growing markets, such as, flat panel displays, cell phones, handheld products, and notebooks. Intersil's product families address power management and analog signal processing functions. Go to <a href="https://www.intersil.com/products">www.intersil.com/products</a> for a complete list of Intersil product families.

\*For a complete listing of Applications, Related Documentation and Related Parts, please see the respective device information page on intersil.com: <a href="ISL9305H">ISL9305H</a>

To report errors or suggestions for this datasheet, please go to www.intersil.com/askourstaff

FITs are available from our website at <a href="http://rel.intersil.com/reports/search.php">http://rel.intersil.com/reports/search.php</a>

For additional products, see <a href="https://www.intersil.com/product-tree">www.intersil.com/product-tree</a>

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/design/quality">www.intersil.com/design/quality</a>

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

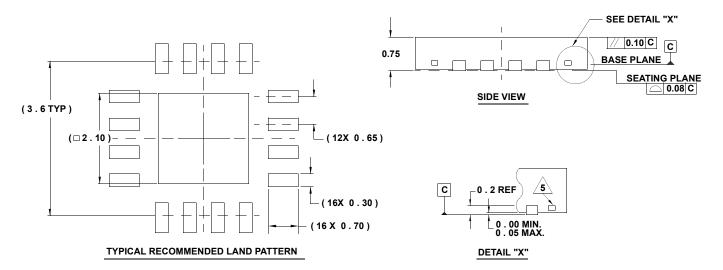

## **Package Outline Drawing**

### L16.4x4G

16 LEAD THIN QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 0, 4/10

### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- ${\bf 2.} \quad {\bf Dimensioning\ and\ tolerancing\ conform\ to\ ASME\ Y14.5m-1994}.$

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- <u>4.</u> Dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 7. JEDEC reference drawing: MO220K.